想象一种情况,CPU直接与主内存通信,没有多级缓存架构,性能将受到重大打击!每次内存访问都会产生显著的延迟,导致程序和应用程序的执行速度变慢。

在高性能计算领域,每纳秒都很重要,因此内存层次结构的复杂性变得至关重要。今天,让我们深入探讨多级缓存的迷人领域,了解它们在提高系统性能方面的关键作用。

L1、dL1缓存:第一(或最后)防线

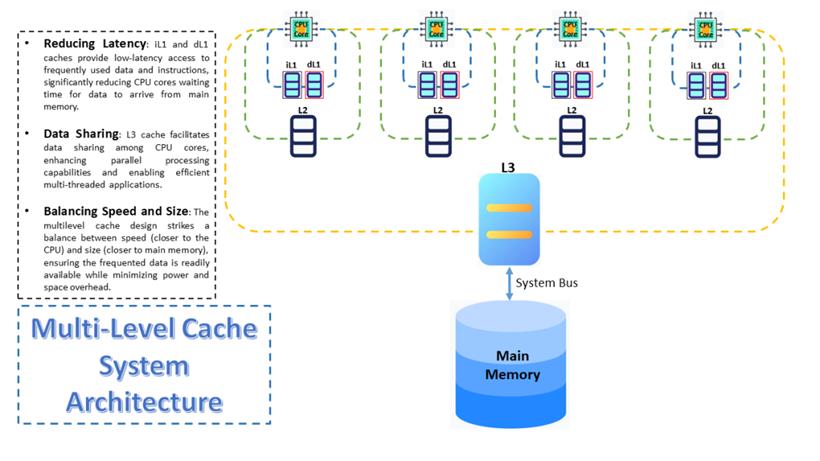

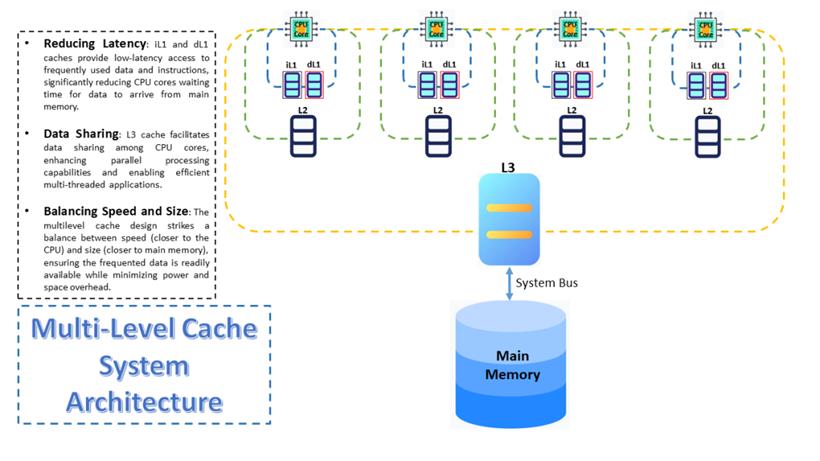

在这个层次结构的核心是指令级1(iL1)和数据级1(dL1)缓存。这些小巧但闪电般快速的缓存位于CPU核心最近,它们的主要作用是存储频繁访问的指令和数据。iL1缓存保存频繁使用的程序指令,而dL1缓存存储计算所需的数据。通常,这种缓存内存的大小很小,大约30-60K字节。访问时间以几个时钟周期来测量,使它们非常快速。可以把它们视为CPU请求的“第一响应者”。

L2缓存:弥合速度差距

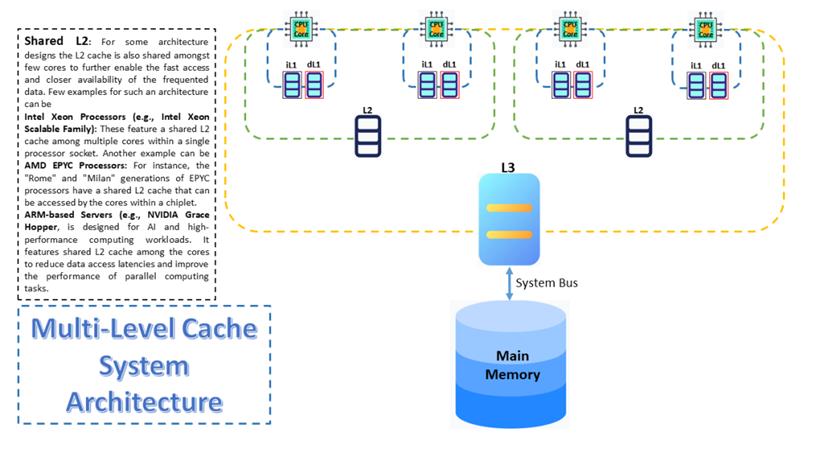

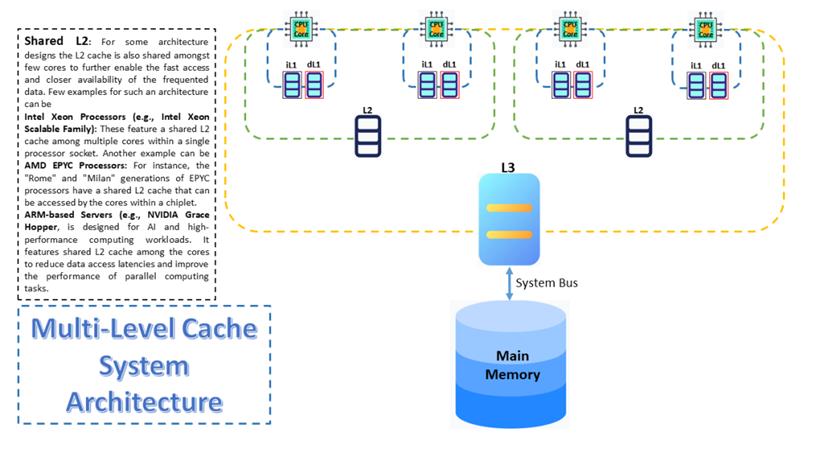

从CPU核心迈出一步,我们遇到了级别2(L2)缓存。L2作为超快的L1缓存和相对较慢的主内存(RAM)之间的桥梁。它的大小更大,可以达到几MB,比L1访问稍慢,但比访问RAM明显快。L2缓存有助于减少内存访问延迟,提供更多存储空间供频繁使用的数据和指令。

L3缓存:全局信息中心

在多级缓存层次结构中,级别3(L3)缓存在多个CPU核心/NUMA/Core Complexes之间共享,通常跨越整个处理器芯片。L3缓存充当全局信息中心,允许不同核心有效地共享数据和指令。它有助于减少核心间通信的延迟,提高整个系统的性能。

在高性能计算中的作用

这些多级缓存在高性能计算中为什么如此重要?答案在于最小化臭名昭著的“内存墙”。随着多年来CPU的速度变得更快,内存访问速度并没有跟上。缓存通过存储频繁使用的数据和指令来弥合这一差距。

在高性能计算中的作用

1.减少延迟: iL1和dL1缓存提供低延迟访问频繁使用的数据和指令,显著减少CPU核心等待数据从主内存到达的时间。

2.数据共享: L3缓存促进CPU核心之间的数据共享,增强了并行处理能力,实现了高效的多线程应用程序。

3.平衡速度和大小:多级缓存层次结构在速度(靠近CPU)和大小(靠近主内存)之间取得平衡,确保频繁访问的数据易于获取,同时最小化功耗和空间开销。

总之,多级缓存架构,包括iL1、dL1、L2和L3缓存组件,是高性能计算的关键因素。它帮助我们的CPU克服了内存延迟等情况,使现代计算体验更加迟缓和低效。

闽公网安备 35020302035485号

闽公网安备 35020302035485号

闽公网安备 35020302035485号

闽公网安备 35020302035485号